## Последовательностные цифровые устройства (ПЦУ)

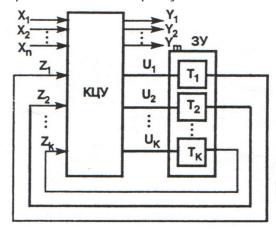

Последовательностные цифровые устройства (ПЦУ) характеризуются тем, что выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. Структурная схема ПЦУ показана на рисунке:

КЦУ — комбинационное цифровое устройство, ЗУ — запоминающие устройство, Т1, Т2 ...ТК — ячейки памяти (триггер), т. е. ПЦУ обладают памятью.

## Триггеры

**Триггер** — простейшее ПЦУ, предназначенное для записи и хранения одноразрядных двоичных чисел.

Входные триггера разделяются на информационные и управляющие. Информационные входы обозначаются следующим образом:

S — вход для установки в состояние «1»;

R — вход для установки в состояние «0»;

J — вход для установки в состояние «1» в универсальном триггере;

К- вход для установки в состоянии «0» в универсальном триггере;

Т — счётный (общий) вход;

D — вход для установки в состояние «1» или состояние «0».

Управляющие входы обозначаются:

V — для разрешения приёма информации (иногда обозначается буквой E);

С — Вход синхронизации.

Триггеры имеют 2 выхода; Q — прямой, Q — инверсный.

Триггеры можно классифицировать по способу приёма информации, принципу построения, функциональным возможностям.

По способу приёма информации триггеры подразделяются

на асинхронные и синхронные. Асинхронные триггеры воспринимают информационные сигналы и реагируют на них в момент появления на входах триггера. Синхронные триггеры реагируют на информационные сигналы при наличии разрешающего сигнала на специальном управляющем входе С, называемом входом синхронизации. Синхронные триггеры подразделяются на триггеры со статическим и динамическим управлением по входу С. Триггеры со статическим управлением воспринимают информационные сигналы при подаче на С — вход уровня 1 (прямой С — вход). Триггеры с динамическим управлением воспринимают формационные сигналы при изменении сигнала на С — входе от 0 к 1(прямой динамический С — вход) или от 1 к 0 (инверсный динамический С — вход).

По принципу построения триггеры со статическим управлением делятся на одноступенчатые и двух ступенчатые. Одноступенчатые триггеры характеризуются наличием одной ступени запоминания информации, двухступенчатые триггеры имеют две ступени запоминания информации. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе.

Двухступенчатый триггер обозначают через TT.

По функциональным возможностям триггеры разделяются на следующие классы:

- с раздельной установкой состояния 0 и 1 (RS триггеры);

- универсальные (JK триггеры)

- с приемом информации по одному входу D (D-триггеры)

- со счётным входом T (T триггеры).

Независимо от вида, если Q = 1 и Q = 0, то триггер находится в единичном состоянии. При Q = 0, Q = 1 состояние триггеры называется нулевым.

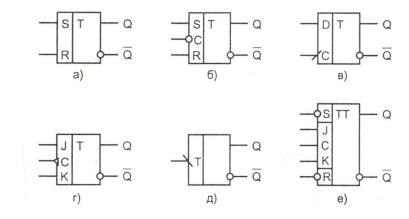

Ниже приведены графические обозначения (УГО) триггеров, принятые в системе ЕСКД:

- А) асинхронный RS синхронный триггер;

- Б) синхронизируемый RS триггер. Синхронизация производится логическим 0;

- В) D триггер, срабатывающий на передний фронт 0,1;

- Г) ЈК триггер, срабатывающий по фронту 1, 0;

- Д) Т триггер, срабатывающий по фронту 1, 0;

- E) двухступенчатый JK триггер со входами разделённой установки в нулевое (R) и единичное (S) состояние.

Функционирование триггеров описывается таблицами переходов (истинности):

Т-триггеры

| Входы | Выходы               |

|-------|----------------------|

| T     | Q                    |

| 0     | исх.                 |

| 1     | $\overline{Q}_{n-1}$ |

## jk-триггеры

| Входы |   | Выходы               |  |  |

|-------|---|----------------------|--|--|

| j     | k | Q                    |  |  |

| 0     | 0 | исх.                 |  |  |

| 0     | 1 | 0                    |  |  |

| 1     | 0 | 1                    |  |  |

| 1     | 1 | $\overline{Q}_{n-1}$ |  |  |

«ИСХ» — означает режим хранения (исходное состояние или без изменения).

«НЕОПР» — означает, что состояние выходов неопределённое, т. е. комбинация сигналов R = S = 1 является запрещённой.

Вт — триггере при T = 1 триггер переходит в инверсивное состояние  $Q_{n-1}$  (счётный режим). В JK — триггере при J = K = 1 триггер переходит в инверсное состояние  $Q_{n-1}$  (счётный режим).  $Q_{n-1}$  — состояние выхода, предшествующее появлению информационных сигналов.

## Регистры

Регистр — это последовательное логическое устройство, используемое для хранения n — разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове (обычно от 4 до 16). На схемах регистры обозначаются буквами RG. Регистр обеспечивает выполнение следующих типичных операций:

- приём слова в регистр;

- передача слова из регистра;

- поразрядные логические операции;

- сдвиг слова влево или вправо на заданное число разрядов;

- преобразование последовательного кода слова в параллельный и обратно;

- установка регистра в начальное состояние (сброс).

Регистры классифицируются по следующим видам:

- накопительные (регистры памяти, хранения);

- сдвигающие

в свою очередь сдвигающие регистры делятся:

о по способу ввода-вывода информации на

- о параллельные,

- о последовательные,

- 。 комбинированные;

- 。 по направлению передачи информации на

- однонаправленные

- о реверсивные

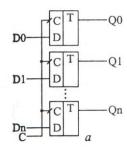

Структура параллельного регистра показана на рисунке:

Основой его являются D — триггеры. Каждый из триггеров имеет свой независимый информационный вход (D) и свой независимый информационный выход. Тактовые входы © всех триггеров соединены между собой. В результате параллельный регистр представляет собой многоразрядный, многовходовый триггер.

D — триггеры на своих выходах повторяют значения сигналов на входах D₀ — D₀ (информационные входы) при действии управляющего сигнала C, т. е. осуществляется параллельный ввод входной информации в регистр.

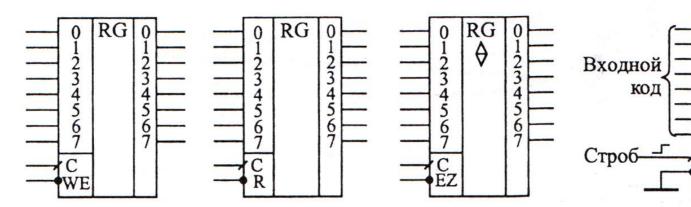

В стандартные серии входит несколько типов параллельных регистров, срабатывающих по фронту:

Различаются регистры количеством разрядов, наличием или отсутствием входа сброса (-R) или разрешения записи (-WE), а также типом выходных каскадов (2С или 3С) и соответственно наличием или отсутствием входа разрешения —EZ. Иногда на схемах тактовый вход С обозначается WR — сигнал записи в регистр.

Представление цифровых данных, каждому биту которых выделена отдельная линия шины, называется параллельным кодом. На рисунке показаны параллельные входной и выходной коды, передача которых

осуществляется одновременно по всем выделенным линиям. Структура сдвигового регистра показана на рисунке:

В сдвиговых регистрах все триггеры соединены в последовательною цепочку (выход каждого предыдущего триггера соединён со входом D следующего триггера). Тактовые входы всех триггеров © объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. В сдвиговом регистре цифровой код представляется временным рядом логических уровней, соответствующих значениям разрядов. Такой код называется последовательным. Каждый бит этого кода передаётся по одной и той же линии. В качестве примера приведем микросхему сдвигающего регистра и его таблицу состояний:

| VOI S S LIDIO                                                      |                                          |    |    |    |    |                                 | · ·          |  |

|--------------------------------------------------------------------|------------------------------------------|----|----|----|----|---------------------------------|--------------|--|

| К1 55 ИР1 3                                                        | R C                                      | SI | S0 | DR | DL | $Q_1 \dots Q_8$                 | Режим        |  |

| 11 C RG                                                            | 1                                        | 1  | 1  | 1  | *  | Q <sub>1</sub> Q <sub>8</sub>   | Параллельный |  |

| 2 — DR RG 22 — DL                                                  |                                          |    |    |    |    |                                 | ввод         |  |

| 23 — S1 Q <sub>1</sub>                                             | 1 _                                      | 0  | 0  | *  | *  | $D_1D_8$                        | Хранение     |  |

| $ \begin{array}{c cccc} 1 & S0 & Q_2 \\ 2 & D1 & Q_3 \end{array} $ | 1                                        | 1  | 0  | *  | 0  | Q2Q8 0                          | Сдвиг влево  |  |

| 5 — D2   Q4                                                        | 1 5                                      | 1  | 0  | *  | 1  | Q2Q8 1                          | Сдвиг влево  |  |

| 7 — D3<br>9 — D4                                                   | 1                                        | 0  | 1  | 0  | *  | 0 Q <sub>1</sub> Q <sub>7</sub> | Сдвиг вправо |  |

| $\begin{array}{c c} 9 & D4 \\ 15 & D5 \end{array}$                 | 1                                        | 0  | 1  | 1  | *  | 1 Q <sub>1</sub> Q <sub>7</sub> | Сдвиг вправо |  |

| 17 D6   Q <sub>8</sub>                                             | 0 *                                      | *  | *  | *  | *  | 00                              | Сброс        |  |

| 19 — D7<br>21 — D8                                                 | Знак * означает любое состояние.         |    |    |    |    |                                 |              |  |

| 21 D8<br>13 PR                                                     | Знак — означает передний фронт импульса. |    |    |    |    |                                 |              |  |

Микросхема К155ИР13 является универсальным восьмиразрядным реверсивным сдвигающим регистром и может работать в режимах последовательного ввода информации со сдвигом вправо или влево, параллельного ввода информации, хранения информации, сброса (установки нулей).

Микросхема имеет следующий вход:

D1 — D8 — для параллельного ввода информации, DR и DL информационные входы для последовательного ввода информации при сдвиге соответственно вправо или влево, входы S1 и S0 — для выбора режима работы, R — вход сброса триггеров регистра в нулевое состояние и С — вход синхронизации.

Сброс триггеров осуществляется при подаче логического 0 на вход R. При S1 = 0 и S0 = 1 осуществляется последовательный ввод информации со входа DR в первый разряд регистра со сдвигом вправо. При S1 = 1, S0 = 0 осуществляется последовательный ввод информации со входа DL в восьмой разряд регистра со сдвигом влево.

При S1 = S0 = 1 осуществляется параллельная запись информации со входов D1 — D8 при воздействии положительного перепада на входе синхронизации С.

При S1 = S0 = 0 осуществляется режим хранения информаци